# Part II: Technical Options for Flexible Hardware-Enabled Guarantees

James Petrie and Onni Aarne *April* 2025

# **About This Report**

This is the second part of a three-part exploration of flexible hardware-enabled guarantees (flexHEGs), commissioned by ARIA. This document can serve as a stand-alone discussion of flexHEGs for technical audiences. Readers who are interested in additional discussion of the motivation of the proposal should read <a href="Part II">Part II</a>, and readers who are interested in uses of flexHEG for international treaties about AI development should read <a href="Part III">Part III</a>.

## **Table of Contents**

| About This Report                            |    |

|----------------------------------------------|----|

| Table of Contents                            | 1  |

| Introduction                                 |    |

| FlexHEG Design Goals                         | 4  |

| Potential Accelerator Modifications          | 7  |

| Hardware Modifications (Integrated)          | 8  |

| Hardware Modifications (Retrofitted)         | 9  |

| Firmware Modifications                       | 10 |

| Software Modifications                       | 11 |

| Accelerator Measurements                     | 12 |

| FlexHEG Hardware Components                  | 13 |

| Guarantee Processor                          | 14 |

| Secure Enclosure                             | 18 |

| Interlock-Based FlexHEG Design               | 23 |

| Repurposing the Network Interface Controller | 24 |

| Encrypted Cluster Formation                  | 25 |

| Cryptography Hardware                        | 26 |

| General-Purpose Workload Guarantees          | 28 |

| Transparent Logging and Auditing                               |    |  |

|----------------------------------------------------------------|----|--|

| Automated Local Scanning of Unmodified Workloads               | 29 |  |

| Compute Graph Declaration                                      | 30 |  |

| Framework-Based Verification                                   | 32 |  |

| Guarantee Example: Multi-Accelerator FLOP Counting             | 33 |  |

| Guarantee Update Process                                       | 36 |  |

| Future Work                                                    | 38 |  |

| Project 1: Tamper-Evident Secure Enclosure                     | 40 |  |

| Project 2: Trustworthy Guarantee Processor                     | 41 |  |

| Project 3: Accurate Compute Graph                              | 42 |  |

| Project 4: Automated Guarantee Checking                        | 44 |  |

| Integration and Deployment                                     | 45 |  |

| Bibliography                                                   | 46 |  |

| Appendix A: Background on Frontier AI Development and Hardware | 51 |  |

| Appendix B: Threat Models                                      | 55 |  |

| Domestic Oversight                                             | 55 |  |

| International Treaty Verification                              | 56 |  |

| International Treaty Enforcement                               | 56 |  |

| Defensive Protection of AI Systems                             | 57 |  |

| How Secure is Secure Enough?                                   | 57 |  |

# Introduction

Frontier AI models could pose serious risks to public safety and international security [1]. Because of these potential risks, it may soon be important for frontier AI developers to be able to make credible guarantees about what AI development they are or are not doing. It would be very useful if AI developers could provide these guarantees without having to reveal proprietary information about how their models are developed.

Frontier AI development depends heavily on specialized hardware - particularly AI accelerators running in massive data centers. These accelerators are a natural node for structuring guarantees about AI development, as a large number of accelerators are needed and their supply chain is highly concentrated [2]. In some contexts, such as domestic regulation, usage of these accelerators could be verified by trusted intermediaries like cloud providers [3]. However, for international agreements about AI development, there may be no entity that all parties would trust with such deep visibility into their AI programs.

To address this challenge, we propose Flexible Hardware-Enabled Guarantees (flexHEG) - a system that uses open source and privacy-preserving hardware to enable AI developers to make verifiable claims about their compute usage. The system would be:

- Privacy-preserving: Developers could verify compliance with guarantees without revealing sensitive details about their work.

- Flexible: The verification capabilities could be updated over time as technology and governance needs evolve.

- Trustworthy: The system would be open source and auditable to provide confidence that it does not contain backdoors.

- Secure: Physical and cryptographic protections would prevent circumvention of the guarantees.

FlexHEG is composed of two main components: an auditable Guarantee Processor that monitors accelerator usage and verifies compliance with specified rules, and a Secure Enclosure that protects against physical tampering. Because both AI technology and governance needs are rapidly evolving, the system is designed to flexibly support many types of guarantees through updateable verification capabilities. The Guarantee Processor could be configured to only accept updates approved by appropriate stakeholders - the implications of this for international governance are analyzed in <a href="Part III">Part III</a> of this report series.

For verification use cases, it is sufficient for the flexHEG Secure Enclosure to be tamper-evident, ensuring that tampering with a large number of devices could not go undetected. For use cases that require guarantees about future accelerator usage, the secure enclosure should also be able to trigger a tamper response that permanently disables the accelerator before an attacker can circumvent the guarantee logic or extract secret keys.

This report explores the technical options for implementing flexHEG, with a focus on approaches that could be deployed relatively quickly. First, we establish concrete design requirements, arguing that it should be auditable, highly secure, and deployable by 2027 to be most useful for emerging AI governance needs (FlexHEG Design Goals). We then review modern AI data centers and AI development workflows that flexHEG must integrate with (Background on Frontier AI Development).

Next, we evaluate different strategies for modifying AI accelerators, from software changes to custom hardware (<u>Potential Accelerator Modifications</u>). We then analyze specific design choices for the two main components - the Guarantee Processor and Secure Enclosure - discussing tradeoffs between security and deployment speed (<u>Hardware Components</u>).

For more robust guarantees, we propose a specific flexHEG architecture that gives the Guarantee Processor direct access to the accelerator's data path (<a href="Interlock-Based Design">Interlock-Based Design</a>). This "Interlock" design enables robust verification without requiring trust in the accelerator's internal operation. Modifying the accelerator's Network Interface Controller (NIC) is a promising strategy for implementing this design that may be achievable by third parties.

Next, we describe concrete approaches to implementing guarantees, from basic auditing to sophisticated automated verification (<u>General-Purpose Guarantees</u>). A detailed example of verifiable FLOP counting for multi-accelerator training demonstrates how these mechanisms could work in practice.

Finally, we outline a roadmap that a major third-party R&D effort could take to develop flexHEG (<u>Future Work</u>). This development could be sped up and directly integrated into existing accelerators with the help of accelerator manufacturers.

# FlexHEG Design Goals

To provide the capabilities required for the use cases discussed in <a href="Part I">Part I</a> and <a href="Part I">Part III</a> of this report series, a full flexHEG system has the following properties (although systems that meet only some of the high-level goals are also useful in more specific contexts):

- Enables AI developers to make guarantees about past and future workloads performed by their accelerators

- Is secure against attempts to circumvent guarantees

- Flexibly allows guarantees to be updated if authorized by the appropriate parties

- Is trusted not to contain backdoors

- Integration doesn't significantly burden model developers

- Can be deployed by 2027 to be included in major data center build outs

To ensure that a given future flexHEG implementation meets these high-level goals, we specify several lower-level requirements, which are summarized in Table 1 and motivated below. The table entry indices are referenced with brackets throughout the text in this section.

| Enables AI developers to make guarantees about past and future workloads | Can execute general-purpose logic     Access to accelerator workload data |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                                                                          | Accurate timekeeping                                                      |

|                                                                          |                                                                           |

|                                                                          | 4. Ability to control accelerator usage                                   |

|                                                                          | 5. Automated guarantee checking                                           |

| Is secure against attempts                                               | 6. Protection against non-invasive attacks                                |

| to circumvent guarantees or exfiltrate data                              | 7. Resistance to invasive attacks                                         |

|                                                                          | 8. Confidential and authenticated communication                           |

|                                                                          | 9. Confidential data storage                                              |

| Allows guarantees to be                                                  | 10. Secure update process                                                 |

| updated if authorized                                                    |                                                                           |

| Is trusted not to contain                                                | 11. No surveillance/control backdoors                                     |

| backdoors                                                                | 12. No intentional security flaws                                         |

|                                                                          | 13. Third-party verifiability of system integrity                         |

| Integration doesn't                                                      | 14. Minimal additional cost                                               |

| significantly burden model developers                                    | 15. Minimal additional power consumption                                  |

| астоюрого                                                                | 16. Compatibility with cooling solutions                                  |

|                                                                          | 17. Standard rack/interconnect compatibility                              |

|                                                                          | 18. Minimal impact on interconnect latency/throughput                     |

|                                                                          | 19. Infrequent false positives                                            |

|                                                                          | 20. Minimal impact on hardware reliability                                |

|                                                                          | 21. Simple to demonstrate compliance with guarantees                      |

|                                                                          | 22. Minimal impact on development workflow                                |

| Can be deployed by 2027 to                                               | 23. Ready for large-scale deployment by 2027                              |

| be included in major data center build outs                              | 24. Compatibility with different types of accelerators                    |

|                                                                          | 25. Short notice integration                                              |

|                                                                          |                                                                           |

Table 1: FlexHEG design goals, separated by category.

# Enables AI developers to make guarantees about past and future workloads performed by their accelerators

The system is able to execute general purpose logic (1) so that it can flexibly perform a variety of guarantees. The flexHEG system has access to accelerator workload data (2) so that it has the necessary information to check guarantees; and accurate timekeeping (3) so that it can support time-based guarantees. The flexHEG system can enable control of accelerator usage (4) so that it can nondestructively enforce that guarantees are adhered to, which is necessary so that a developer can credibly make guarantees about future usage of accelerators. Guarantees can be checked in an automated way (5) so that guarantee checks can be performed in a sufficiently short time, and model details do not need to be shared with auditors (i.e. a hardware-backed zero-knowledge proof).

#### Is secure against attempts to circumvent guarantees or exfiltrate data

The flexHEG system is secure against non-invasive attacks (6) so that guarantees cannot be circumvented with scalable attacks. The system is resistant against invasive attacks (7), with either tamper evidence to disincentivize covert adversaries, or a tamper responsive enclosure that can trigger permanent accelerator disablement to disincentivize overt adversaries. Defense against overt adversaries is required so that guarantees about future usage are a credible commitment that cannot be skipped later by physically disabling the guarantee system. A more detailed exploration of the type of attacks we hope to defend against is provided in <u>Appendix A: Threat Models</u>.

Communication between flexHEG systems is confidential and authenticated (8) to prevent network snooping being used to circumvent guarantees about how data is shared, and so that multiple flexHEG systems can coordinate around guarantees which pertain to many-accelerator workloads. Additionally, accelerator and flexHEG data at rest can be stored in a confidential way (9) so that guarantees cannot be circumvented by an adversary obtaining data with e.g. scanning equipment, and claims from a flexHEG system cannot be falsified using a stolen key.

#### Allows guarantees to be updated if authorized by the appropriate parties

FlexHEG guarantees and the logic to check them can be updated if and only if the update has been authorized by a sufficient number of pre-specified stakeholders (10). Different types of updates could require approval from different stakeholders, and could depend on other conditions being met. Updates could potentially modify the rules for accepting future updates.

#### Is trusted not to contain backdoors

FlexHEG must be trusted to not contain backdoors for secret surveillance or control (11), or intentional security flaws (12) that would allow insiders to circumvent guarantees. Additionally, it is possible for third parties to verify that the flexHEG system is operating as expected (13).

#### Integration doesn't significantly burden model developers

Integration of flexHEG capabilities should not create significant burdens for AI developers. The addition of flexHEG hardware should not significantly increase the total datacenter cost (14). Additional power consumption should be minimal (15). The system is ideally compatible with both air and liquid cooling solutions without significantly increasing the thermal resistance (16). The flexHEG form factor should fit within common server configurations and maintain compatibility with existing interconnects (17). Interconnect latency and throughput should not be significantly impacted for relevant workloads (18). False positives in tamper detection or guarantee checks should be rare (19) to avoid disruptions. Accelerator reliability should not be substantially reduced (20), either by allowing regular maintenance, or by modifying configurations to tolerate partial hardware failure. Demonstrating compliance with guarantees should not be overly time consuming (21). Finally, flexHEG should not significantly impede development or debugging workflows (22).

#### Can be deployed by 2027 to be included in major data center build outs

Massive data center build outs are planned between 2025-2030 [4], [5], and AI development past 2030 may occur on the same hardware and infrastructure, even if transformative AI is several years later. In order to reach its full potential, flexHEG systems will likely need to be deployed at scale by 2027 or sooner (23). Additionally flexHEG should be compatible with the different types of accelerators (24) that are used by frontier AI developers, ideally on short notice (25) for cases where countries were not able to collaborate years in advance of a treaty.

# **Potential Accelerator Modifications**

In this section, we discuss four ways that AI accelerators could be modified to meet the flexHEG design goals, with tradeoffs between security, time to readiness, and sophistication of guarantees. For more background on frontier AI workloads and the data center hardware they run on, refer to <a href="https://example.com/appendix A">A</a> for a brief summary.

Accelerators could be modified to include flexHEG capabilities using integrated flexHEG components, retrofitted flexHEG components, firmware modifications, or software modifications. Including flexHEG directly in the accelerator die or PCB would provide the

<sup>&</sup>lt;sup>1</sup> What counts as a "significant" burden depends on the context, but as a rough guess this might be a 1-2% percent increase in cost in typical scenarios, 5% if needed to satisfy regulations, and 20% if there is high-level buy-in.

greatest design flexibility but would take the longest to deploy. To speed up deployment, flexHEG components could be separately manufactured and retrofitted to existing accelerators. Finally, firmware and software changes are the fastest to deploy, but rely on the limited hardware security that is already on devices. The advantages and disadvantages of these options are discussed below.

## Hardware Modifications (Integrated)

Specialized flexHEG hardware could be integrated directly into the accelerator PCB or main chip, which would provide the best security and data access. If the Guarantee Processor is on the main chip, it would be much more difficult for attackers to modify signals that stay within the chip. Additionally, supply chain attacks that divert a fraction of components before adding a Guarantee Processor would be more difficult to execute (because the Guarantee Processor would be on the same mask). A purpose-built Guarantee Processor could be designed to prioritize security and auditability, as discussed in the Guarantee Processor section.

The Secure Enclosure could also be added at the chip level, which may improve security by reducing the size of the attack surface (however, it may still be important to also have a larger secure enclosure that prevents direct access of tools to the chip surface).

If flexHEG hardware were deeply integrated throughout an accelerator, it may be more difficult for an attacker to physically disable it. However, deep integration would make external audits challenging and reduce portability to other accelerator types. A potential solution is to have dedicated blocks within the hardware for the Guarantee Processor that can be open sourced for external audits.

There are three operational downsides to integrated hardware changes:

- They require significant assistance from the accelerator manufacturer, which could cause challenges due to, among others, proprietary IP.

- They likely require years of preparation to add to each type of accelerator (among others due to multi-year-long manufacturing cycles).

- They cannot be added to existing accelerators, which is a downside both for the absolute year they could be available, and for last-minute integration into novel accelerator types.

The lag time for hardware- integrated flexHEG depends on the time for it to be designed and manufactured, and the time for older compute to be displaced. An investigation by Epoch AI, a research institute focused on analyzing key trends in AI, suggests that, counting from the time a new hardware generation is launched, it would take 2.7 - 3.9 years for the old accelerator generation to no longer be useful for frontier development (see Figure 2) [6]. If the current trend

for deployed compute slowed<sup>2</sup>, this estimate would increase (because it would take longer for prior compute to be displaced). Additionally, as a rough estimate<sup>3</sup> it might take 1-4 years to add changes to all leading accelerator designs. Overall, this estimate predicts 3.7 - 7.9 years for flexHEG with integrated hardware to displace non-flexHEG accelerators in frontier AI development (starting when the accelerator manufacturer begins actively working on it).

Figure 2: Installed NVIDIA computing power by accelerator generation over time. Source: Epoch AI [6].

## Hardware Modifications (Retrofitted)

If the modifications can instead be retrofitted to existing accelerators, the time to deployment and reliance on accelerator designers can be reduced. Retrofittability may be especially important if flexHEG needs to be quickly added to accelerators used by countries that are not allowed to purchase the newest generation of NVIDIA chips. Because retrofitted hardware is added after manufacturing, additional supply chain security may be needed. Compared to integrated hardware, retrofittable hardware may be easier for an attacker to decouple from the accelerator. This can potentially be defended against with a retrofittable Secure Enclosure, which is discussed in more detail in Secure Enclosure.

<sup>&</sup>lt;sup>2</sup> It's unclear whether this exponential growth in compute will continue past 2030 because it would start to reach a significant fraction of electricity production [7] (and predictions for AI trajectories more than five years in the future are difficult to make confidently).

<sup>&</sup>lt;sup>3</sup> Nvidia does not publicize their engineering design timelines, but some sources say major architectural modifications take 3 years from design to rollout.

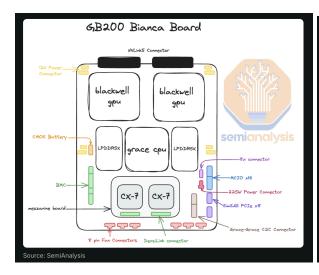

One option to retrofit a Guarantee Processor is to add it as an additional component that can make external measurements, as done with the power-measurement prototype. To get additional data access, the Guarantee Processor could potentially be plugged into an open PCIe slot (for example, NVL72 trays have 8 slots for PCIe drives, which may not all be used [8]). Nvidia supports third party direct memory access to HBM [9], so a third-party device could potentially be set up to read from HBM<sup>4</sup>.

Similarly, an existing retrofittable component on the accelerator could be replaced with a flexHEG version. For example the Network Interface Controller, or Hardware Management Controller (also called BMC) could be replaced to function as the Guarantee processor, as discussed in <u>Guarantee Processor</u>.

#### **Firmware Modifications**

Firmware is code that runs on computing devices and is generally responsible for lower-level device functioning. Several components within an accelerator will typically have their own firmware. A security advantage of firmware over software is that devices that have Secure Boot [10] can only run firmware that has been cryptographically signed by the manufacturer (as opposed to software, which can be easily modified or replaced). Devices that also have Rollback Protection [10] can only run firmware binaries that have a version number that is greater than a value stored in secure memory. Additionally, because firmware can run directly on the AI chip, it has the same security benefit as integrated hardware that signals are more difficult to tamper with.

There are several components on existing accelerators that could potentially be reprogrammed with a firmware update to support flexHEG logic. Components used for compute, networking, and memory could potentially be repurposed, with different tradeoffs between feasibility, security, and the types of guarantees that could be supported. These options are discussed in more detail in the Guarantee Processor section. One downside is that it may be more difficult (compared to using a dedicated Guarantee Processor) for auditors to verify that firmware on a proprietary chip is functioning as intended.

As a relatively simple example, it may be possible to create modified firmware for existing accelerators that would require occasional authorization from the manufacturer or a regulator in order for the accelerator to continue operating [11], [12], [13]. By combining this with verification software (discussed in next subsection), it could be possible to structure guarantees

<sup>&</sup>lt;sup>4</sup> Although there are some security risks with this because a sophisticated actor may be able to spoof PCIe reads that have to physically route through multiple components. As another potential limitation, the current implementation of confidential computing blocks direct memory access from third party devices, which may have to be modified to support this use case (this might have to be done by Nvidia anyways to support efficient multi-node confidential computing).

about future usage without making hardware changes. I.e., receiving updated licenses permitting accelerator usage could be contingent on auditors having received evidence that ongoing accelerator usage met the guarantees.

While firmware with Secure Boot can be more challenging to circumvent than software, it is not completely resistant to physical attacks. The most common of these attacks is to modify or replace the firmware, then apply a voltage glitch at the exact time during Secure Boot when the cryptographic signature is being checked<sup>5</sup> [14]. For devices without protections against voltage glitching, this can cause the signature check to incorrectly pass, allowing the use of unauthenticated firmware.

Accelerator designs are generally proprietary and Secure Boot requires firmware changes to be signed, so firmware updates would likely require substantial assistance from chip designers. Several different manufacturers make components that are on each accelerator, so this would not necessarily require assistance from the primary accelerator designer.

#### **Software Modifications**

The most straightforward strategy for third-parties to execute guarantee logic is to create software that runs on the CPUs that are responsible for managing the accelerators. Verification of the software that is run can be provided by Trusted Execution Environments (TEEs) [15], which use a hardware root of trust to provide difficult-to-fake evidence that the computing environment is configured as claimed. Mithril Security [16] and EQTY Lab [17] are currently working on strategies like this with the goal of providing a credible record of how a model was trained. EQTY's whitepaper describes their approach in more detail, but at a high level, hardware security keys from the CPU and GPU are used to sign a record of the software initially loaded on the device, and a session key that signs any data or code that is later loaded for training. If an auditor is provided with detailed logs containing all of the software and data used, these signatures provide evidence that the software was executed as claimed in a specific computing environment. The signatures are difficult to fake because the hardware keys are stored in secure hardware memory.

At the time of writing, Nvidia has released an early-access implementation of Confidential Computing (based on a TEE managed by the host CPU). The early access implementation supports a single node with AMD or Intel CPUs, but does not yet support multi-node or Grace CPUs (which limits the possibility for immediate widespread deployment). Nvidia's Confidential Computing implementation doesn't currently claim to be secure against sophisticated physical tampering. Additionally, security is one of many sometimes conflicting priorities for high-performance CPUs, and significant non-invasive TEE vulnerabilities are sometimes discovered [19], [20].

<sup>&</sup>lt;sup>5</sup> There are also common defenses against fault injection attacks, like repeating important steps several times in series or in parallel to be able to detect inconsistencies.

Using a TEE makes it more difficult to falsify workload records, but does not prevent developers from using different software without any guarantees built in. For this reason, software-based solutions could enable verification about how hardware has been used, but would not be able to enforce that the hardware cannot be used in guarantee-breaking ways.

TEE-based proof of training could be implemented in the near-term by sharing workload logs with auditors so they can manually check that the workload is compliant. More advanced designs may be able to automate this verification process so that AI model details do not have to be revealed. These automated checks could be done in a few ways, including: 1) providing developers with an API for model development that blocks non-compliant workloads 2) inferring workload characteristics by scanning code and gathering usage data 3) allowing developers to make specific claims about why their workload is compliant, and more narrowly verifying these claims. We explore these options in more detail in <a href="General-Purpose Guarantees">General-Purpose Guarantees</a>. If the workload passes the check, the session key can be used to sign a certificate stating that the model passed without needing to reveal additional details. Progress on automated guarantee checks in software would likely translate to hardware-based solutions if the same workload information is available. With a lower barrier to entry, this makes TEE-based software a promising development environment for automated guarantee checks that are eventually intended to run on dedicated hardware.

Overall, TEE-backed software for workload verification is relatively fast to deploy, but probably not secure against sophisticated actors if they have unrestricted physical access. This limited security may be sufficient for domestic regulation, where it could be difficult to hide major efforts to attack verification mechanisms. In international contexts, TEE-backed software could provide verification capabilities while more trusted hardware is developed. This could be made more secure if combined with tamper evidence, national intelligence agencies searching for circumvention attempts, and additional sensors collecting measurements to corroborate claims.

## **Accelerator Measurements**

Several data sources could be used to verify workload guarantees, with different sources enabling different types of guarantees. The following table lists potential data sources and their respective advantages.

| Accelerator<br>Memory (HBM) | Direct memory access would provide visibility into workload state. This access could enable verification of claims about model architecture and |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | facilitate snapshots of accelerator state for auditing.                                                                                         |

| Accelerator<br>Instructions | If the accelerator is trusted to execute instructions, monitoring the kernels sent to the accelerator could enable analysis of workload characteristics.  One limitation                                                                                                                                                                                                                                             |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Network Traffic             | For distributed workloads, monitoring inter-accelerator communication could provide important information about the overall computation being performed. This could also be useful for guarantees about the network configuration.                                                                                                                                                                                   |

| Performance<br>Counters     | Hardware performance counters could provide metrics such as FLOP counts, memory access patterns, and interconnect utilization.                                                                                                                                                                                                                                                                                       |

| Power Usage                 | Power consumption monitoring offers a data source that is difficult to falsify without physical modifications. Power signatures could help identify workload types and detect anomalous computation patterns. Additionally, power measurements could serve as a cross-validation mechanism to verify consistency with other reported metrics. An existing FlexHEG prototype uses high resolution power measurements. |

Data sources that are consistent across different accelerator types are preferable, as they reduce the amount of customization needed for each hardware platform. Using multiple independent data sources could improve the robustness of guarantees, since attackers would need to falsify all sources to avoid detection. The availability of these measurements depends on how the Guarantee Processor connects to the accelerator, while their trustworthiness is determined by whether the measurement occurs within the Secure Enclosure and how much it relies on components that are vulnerable to attack or difficult to audit. As discussed in the <a href="Interlock section">Interlock section</a>, placing the Guarantee Processor on a critical data path for accelerator usage is one option to improve the trustworthiness of measurements.

# FlexHEG Hardware Components

In this report, we mainly focus on flexHEG implementations that use a Guarantee Processor to collect accelerator data and perform guarantee checks, and a Secure Enclosure to protect the guarantees from being circumvented with physical tampering. The Guarantee Processor and Secure Enclosure are intended to function separately from each other to make the design and deployment process simpler, and also because in some scenarios it may be important for separate parties to design and manufacture these components. This section analyses requirements and tradeoffs for the Guarantee Processor and Secure Enclosure.

#### **Guarantee Processor**

With an on-device Guarantee Processor, checks can be done locally in a privacy-preserving way where sensitive data does not need to leave the device. The Guarantee Processor could simply provide a cryptographically signed certificate saying that the guarantee has been met, which the device owner could use as credible proof if they choose to. Additionally, a dedicated guarantee processor can be much more auditable than a full accelerator system, because it can be smaller, simpler, less performance sensitive, and would be possible to open source without revealing trade secrets. This is especially advantageous for being able to add it to untrusted accelerators.

As previously discussed, it is important that the Guarantee Processor have robust access to accelerator measurements. In addition, the guarantee processor ideally:

- Is performant enough to execute the guarantee calculations discussed in General-purpose Guarantees. For example, it would be useful for the Guarantee Processor to be able to double check the work of one Streaming Multiprocessor (SM) on a Blackwell chip, which would require roughly 1/192 the computational power of a Blackwell chip (because they have 192 SMs)

- Is secure against cyber attacks that might attempt to make use of flaws in the implementation.

- Is secure against physical attacks that might make it through the secure enclosure

- Is able to perform necessary cryptographic algorithms, and can do so without revealing information via side channels like timing or power. A special case of this is when the Guarantee Processor is responsible for efficiently encrypting the data stream, as discussed for the <a href="Interlock Cryptography Hardware">Interlock Cryptography Hardware</a>. Public key cryptography is also needed for verifying the authenticity of updates and for signing certificates about which guarantees have been met. This public key cryptography is ideally quantum secure (e.g zeroRISC's work for Secure Boot [22])

- Is auditable by third parties that might not trust the designers or manufacturers

- Is possible to update if and only if authorized by the required parties (see <u>Guarantee Update Process</u>).

- Has access to a reliable real-time clock for time-dependent guarantees.

- Has access to a secure random number generator.

There are several existing processor IP blocks that could be used to satisfy at least a minimal version of these requirements, including a range of TPM cryptoprocessors [21]. As an example of a related (although closed-source and obfuscated) processor, the Intel Management Engine is included on many Intel CPUs for features like anti-theft prevention and capability licensing [22]. There are also open-source alternatives [23], [24], [25].

To increase trust that backdoors have not been added to the Guarantee Processor design or manufacturing process, some options are:

- Open-sourcing the guarantee processor design and guarantee logic, which could then be analyzed and compared with physical scans of randomly selected chips.

- Using FPGAs to execute some or all of the guarantee logic, because they can have their configurations publicly audited, might be easier to check for physical inconsistencies because of their more uniform structure, and can use variants of configurations with equivalent logic to make many hardware trojans impractical [26].

- Sourcing multiple guarantee processors from different manufacturers<sup>6</sup> and running the same instructions on all of them before checking their outputs for consistency on-device (this approach is similar to the Lock-Step, which is used to provide fault tolerance in functional safety designs [27]). With three guarantee processors, they could detect disagreements and use ¾ voting to choose which action to take.

The guarantee processor should be able to defend against voltage glitching and similar attacks [28]. There are also manufacturing techniques that would probably make tampering harder if an attacker is able to circumvent the secure enclosure (e.g., putting the guarantee processor near sensitive or fragile components like tamper sensors or interconnect channels). The FIPS-140-3 certification measures the security of similar hardware security modules, and a similar certification process could potentially be used for the Guarantee Processor.

A dedicated Guarantee Processor could be added to future accelerators as a standalone chiplet, or as a part of another die. Alternatively, for a retrofittable solution, it could be added to existing accelerators as a plug-in device (e.g. using a PCIe slot that can be configured to read from HBM with Direct Memory Access (DMA) [9]).

As mentioned in the <u>Firmware Modifications</u> section, several components on existing accelerators already have general-purpose processors that could be updated with manufacturer assistance. Repurposing existing components would make deployment much easier, but may require compromising on some of the previous requirements. Some options for components to repurpose are analyzed in the table below.

# Processor(s) on AI chip

AI chips often have reprogrammable processors directly on the main die. The designs are generally proprietary, but these processors are likely used to handle tasks related to general chip management, security and data processing. Nvidia reportedly has 10-40 cores on each GPU that are based on the open-source RISC-V architecture [29]. Some of these RISC-V cores power the GPU System Processor, which is responsible for communication with the CPU kernel driver, and "has full access to everything in the GPU, including access to the memory controllers". Security logic on these microcontrollers appears to be formally verified [30].

<sup>&</sup>lt;sup>6</sup> Although this may increase the risk of a single compromised guarantee processor being used to sabotage chip usage.

|                                    | Processors on AI chips are especially promising for implementing guarantees because they have direct access to the chip state, and being on the same die makes them more difficult to tamper with.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| High<br>bandwidth<br>memory        | High bandwidth memory (HBM) is used in AI accelerators to store workload state (e.g. model weights and gradients). Currently HBM doesn't have significant (or potentially any) on-chip reprogrammable computing ability, but major HBM designers (e.g. Samsung and HK-Synx) are attempting to add it. HBM-PIM (Processor In Memory) and HBM-PNM (Processor Near Memory) are two proposed designs that would allow some accelerator computations to be performed without leaving the HBM block, which could improve efficiency.  If on-die processors were added to future HBM chiplets, they would be a                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                    | <ul> <li>They have direct access to workload state</li> <li>HBM is difficult to manufacture and is an important part of all leading accelerators</li> <li>They would be simpler and more transferable between accelerator types than many other components in the accelerator system</li> <li>They could take snapshots of memory</li> <li>They could randomly check accuracy of a fraction of computations and data transmissions to verify that other untrusted hardware is acting as claimed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Network<br>interface<br>controller | Network interface controllers are used to handle communication between each accelerator and the scale-out network. Modern NICs like Nvidia's ConnectX-8 have programmable compute capabilities for "in-network" processing and hardware for inline cryptography, while being able to process up to 800Gb/s (100GB/s) of data. NICs are an important part of datacenter security because they can encrypt data that leaves each node, protecting data in transit from being read or modified.  NICs can directly observe the data sent through them to the broader network. They can also use Direct Memory Access (DMA) to read the contents of HBM.  The NIC's architecture is typically simpler than a CPU, which can reduce its attack surface, and its position at the interface between the network and compute node creates a natural security boundary. Amazon's Nitro system leverages this approach [31], using NICs as hardware-backed security boundaries to isolate virtual machines by offloading security-sensitive |  |

operations. Other companies implement similar security strategies with NICs, though with less public documentation.

NICs are well situated to observe workloads that involve many accelerators because they sit on the main data path for communication between accelerators across nodes. This strategic position, combined with the ability to swap out the NIC with one made by a different manufacturer (as Amazon is doing with their NVL72 systems [32]), makes NICs a strong candidate for implementing flexHEG logic.

#### Datacenter Secure Control Module

Datacenter Secure Control Module (DC-SCM) is a standard for a module used to perform server management and provide security functionality [33], [34]. NVL72 is mostly compatible with the DC-SCM standard (the form factor is slightly smaller but the electrical interfaces are the same<sup>7</sup>).

DC-SCM is plugged in via PCIe rather than built directly into the motherboard like typical baseboard management controllers (BMCs). This allows reuse of components across different motherboards, and enables data center operators to replace the module without replacing the entire motherboard (e.g., if a hardware update is needed for security reasons). DC-SCM might be a relatively simpler option for implementing flexHEG logic because:

- It is less critical for accelerator performance, so might be more feasible to modify without disruption

- It would be relatively easy to replace with a dedicated flexHEG version

- They already have access to information about the board like power usage

- As a PCIe device, it may be possible to configure read access of HBM One downside of DC-SCM modules, however, is that they are not on the main data path, so data readings may be easier for an attacker to spoof.

Other components on or connected to accelerators within data centers could potentially be repurposed for flexHEG, including network components like switches. It is also an option to repurpose multiple components, which could provide defense in depth and more comprehensive information (although for simplicity, we will not discuss this option more here). To make auditing and design simpler and faster, it may make sense for a submodule within a component to be used for flexHEG, rather than the entire component.

<sup>&</sup>lt;sup>7</sup> "We also developed a new, denser DC-SCM (Data Center Secure Control Module) design that's 10% smaller than the current standard" [35].

In the Interlock section, we analyze a specific design where data entering and leaving the accelerator must pass through the Guarantee Processor (or rather a buffer that it has direct access to).

#### Secure Enclosure

A secure enclosure is used to protect flexHEG devices from physical tampering. This is needed, because otherwise an adversary could modify hardware to circumvent guarantees, or use measurements to exfiltrate confidential data. Depending on the threat model (see Appendix B for more on threat models), there are different ways to dissuade tampering, including using a tamper evident enclosure, or a tamper-responsive enclosure that triggers disablement of the accelerator. Another option that is a mixture of tamper evident and tamper responsive is to incorporate a Physically Unclonable Function (PUF) in the enclosure, where tampering with the enclosure would corrupt the measurements used to derive a secret PUF key. Without the PUF key, adversaries would not be able to sign attestation certificates or decrypt important data. The secure enclosure boundary could potentially contain a single chip, a single accelerator PCB, several accelerators within a tray, many accelerators within a rack, or even larger configurations. The choice of where to put the security boundary has several tradeoffs between security, maintenance, and time-to-readiness. It also influences where flexHEG logic can be securely executed, and where encryption is needed (e.g. if chip-level security boundary, ideally want to encrypt data leaving the chip). In this section, we summarize publicly available information on hardware security that is relevant for AI accelerators and flexHEG threat model, and also how trade offs here influence the overall flexHEG design.

Secure enclosures have been used for decades to defend cryptographic coprocessors and other chips from physical tampering [36], [37]. The FIPS-140 certification process [38][12] measures the physical defenses of tamper-responsive enclosures for cryptographic coprocessors. At the time of this writing, there are four devices with the maximum FIPS-140 rating (level 4) that are sold by IBM [14] and by Private Machines [15]; neither of the systems have much public information about their tamper resistant security features, likely because security-by-obscurity is commonly practiced in hardware security, which is more offense-dominant than cryptographic security. The IBM and Private Machines devices have not been publicly broken<sup>8</sup>, although it is unclear how secure they would be against state-backed actors. There are also rumors of private US government projects on hardware security that may have even more advanced defensive measures. Hardware security from these related domains could potentially be translated to work with AI accelerators if it can be modified to accommodate the accelerator form factor(s) and to handle high heat dissipation.

Tamper-evident enclosures could be useful in scenarios where accelerators can be inspected and where misuse does not need to be prevented immediately. Building tamper-evident enclosures

<sup>&</sup>lt;sup>8</sup> Though an older IBM cryptographic coprocessor was broken [39].

could potentially be faster and simpler than tamper-responsive enclosures (they probably do not require a battery or self-destruct mechanism). Techniques used for monitoring nuclear materials, like tamper evident seals and 24-7 video cameras could be fairly simple to adapt to this use case (and data centers typically already have these cameras). Some of the older tamper-evidence techniques may not be perfectly secure, like the cold-war seals that can apparently be broken [40]. However, this type of tampering would probably be difficult to perform on a large fraction of accelerators in a data center without being detected. The security could also be improved by layering different types of tamper resistance and tamper evident defenses.

Physically unclonable functions (PUFs) are usually used to provide persistent secret information that cannot be passively measured with scanning equipment. PUFs do this by taking measurements of unique hardware characteristics and using them to generate a secret key. This is normally done with components like SRAM PUFs [41], but the same principle could be used for a secure enclosure. For example, the PUF could be based on electrical properties of a conductive mesh that is embedded in the enclosure wall.

An advantage PUFs have over active sensing is that they don't require a battery. However there are also a few limitations to PUFs:

- The PUF key generation procedure might take seconds, so might be too slow to respond to some attacks without also pairing active sensing (closer to millisecond response time)

- To use PUFs to prevent future usage of accelerators that have been tampered with, the destruction of the secret key must prevent decrypting data that the accelerator cannot operate without. This could potentially be the firmware or tuned coefficients for the accelerator, which would make it difficult for adversaries to use the accelerator if they do not have a functioning version of the firmware or tuning procedure. Against sophisticated adversaries, this may not be sufficient though, because they would only need to acquire this firmware once to unlock all of their devices, and this firmware could potentially be leaked by a single rogue employee that works for the accelerator manufacturer.

- While PUFs make passive scanning of secret information difficult, when that secret information is read in order to recreate the secret key, that information is transmitted on data buses and stored in registers. These registers and buses could potentially be read with microprobing or laser voltage probing. One strategy used to mitigate this is using a "strong PUF" that has enough entropy to generate many keys, so that the same information doesn't need to be read repeatedly. However, being able to generate many different keys does not immediately solve the problem, because the secret information on device needs to be encrypted and decrypted with a particular key, so to do this locally would require multiple reads of the same key. A different defense that enclosure PUFs could use against active scanning of registers is to design the physical enclosure in such a way that signal wires and registers are not possible to access for scanning without first destroying the PUF.

Tamper responsive enclosures use active sensing to detect if the enclosure has been breached and then to trigger an appropriate response. One approach for active sensing is to measure the capacitance of a serpentine-patterned conductor embedded around the enclosure [9]. Similarly, the resistance of a conductor mesh can also be measured [10]. If the mesh is disrupted, then the measurements will change, alerting the tamper-detection system. Measurements of the radio response function within an enclosure could also be used [11] (although detection tests for the referenced prototype have so far only been done with metallic probes). Additional sensors can be used to prevent more sophisticated attacks by measuring for radiation, voltage glitching, lasers, temperature, and the rate of temperature change. To avoid having a single point of failure that could be targeted by an attacker, a distributed network of sensors could be used to independently trigger the tamper-response mechanism.

The appropriate tamper response mechanism depends on the threat model. If the goal is to prevent confidential data from being stolen, it is important to delete all data and secret keys when tampering is detected. Additionally, it is also important to communicate that this tampering has happened, so that the same accelerator is not used again later after it may have been compromised. One option for this is for each accelerator to frequently send an "all OK" signal, and to investigate accelerators that do not send this signal on schedule.

If the goal is to prevent tampering being used to circumvent guarantees about future accelerator usage, tampering should trigger permanent disablement of the accelerator before the guarantees can be disabled. There are multiple approaches that could be used to disable an accelerator. Some options are:

- Capacitors for voltage-based destruction: Large capacitors could be charged during

normal operation and then discharged to apply excessive voltage to critical components

of the chip when tampering is detected. This voltage surge would exceed the chip's

electrical tolerance, causing permanent damage to vulnerable circuit elements. This

approach could be implemented with relatively simple circuit additions to existing

designs and doesn't require changes to the main accelerator die, making it a good option

for retrofitting.

- Embedded antifuse bits: Modern chips can include one-time programmable (OTP) memory cells based on antifuse technology. Unlike regular fuses that start connected and can be blown to disconnect, antifuses start disconnected and can be permanently connected by applying a high voltage. By embedding thousands or millions of these bits throughout the accelerator chip and designing the chip to require specific antifuse configurations to function properly, tampering detection could trigger widespread antifuse activation that would render the chip permanently inoperable. This approach is highly effective but requires deep integration during chip design and manufacturing, making it unsuitable for retrofitting to existing accelerators.

Nanothermite-based destruction: A more experimental approach involves embedding

reactive materials like nanothermite (a material that can produce a rapid exothermic

reaction) on the chip surface. If tampering is detected, the nanothermite could be ignited

by a small electrical pulse, generating intense localized heat that would physically

destroy critical chip components.

To ensure system integrity over the lifetime of the device, a battery inside or outside of the enclosure can be used so that the sensors continue to operate even if external power is disconnected.

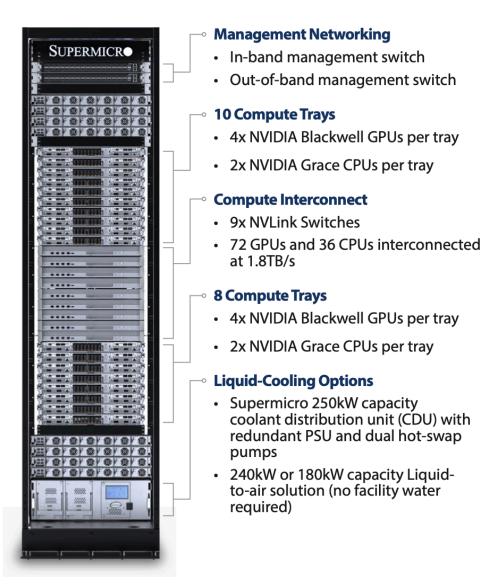

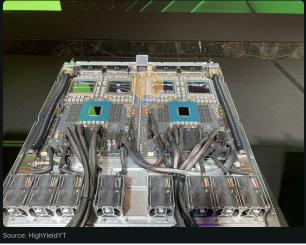

Cooling is necessary for AI accelerators, which have to dissipate up to 1200W of heat per chip (Nvidia B200). Most existing data centres use fans to air cool chips, but some next generation accelerator racks like the NVL72 require direct-to-chip liquid cooling in order to achieve the intended compute density (trays with air cooling are taller than trays with direct to chip liquid cooling). High compute density allows for shorter interconnect cables, which reduces communication latency and cabling cost. Secure enclosures can ideally be made compatible with both air and direct to chip liquid cooling (and potentially two phase direct to chip cooling which is speculated to be the next advancement [42]).

To permit cooling, the secure enclosure boundary can either be sandwiched between the chip face and cooling pad, or it can contain both the chip and the cooling pad. If it is sandwiched beneath the cooling pad, it has to be very thin and very thermally conductive. Alternatively, if it is further away from the chip face, the secure enclosure has to allow heat to flow through it. For air cooled units, this would probably have to allow airflow to pass through the boundary. The security risk of having holes in the enclosure could potentially be reduced by making the air pass through a metalized foam that doesn't permit a direct line of sight into the enclosure, and whose particular geometry is sensed by radio. For direct to chip liquid cooling one option is to have the liquid tubing pass through the enclosure boundary, potentially with a similar defensive layer that allows liquid though. Alternatively, the liquid tubing within the enclosure could form a closed loop, and heat could be exchanged at the enclosure boundary with a liquid-liquid heat exchanger.

Larger enclosures that contain more accelerators are likely faster to design and deploy because they do not need to be as tightly integrated with the specific accelerators (as an extreme example, the "secure enclosure" could be an entire datacenter). Ease of deployment is further improved if the secure enclosure matches standard dimensions for a server tray or rack, like the open sourced MGX rack standard used by NVL72 [43]. However, enclosing multiple accelerators has potential downsides:

The more accelerators in each secure enclosure, the higher the probability that one of them will fail or require maintenance, and for security reasons it would be preferable to not be able to open the enclosure after it has been closed • An attacker would only need to disable one enclosure to access multiple GPUs, and a larger surface area has more room for flaws

To put many accelerators within a single secure enclosure that cannot be opened would be feasible if hardware failure requiring maintenance or replacement was extremely rare. Alternatively, the number of accelerators within the secure enclosure could be over-provisioned, so that the combined system could still function after a few hardware failures (as is done with solid state drive memory regions). The feasibility of over-provisioning depends on the software and network architecture. This is simpler for hub-and-spoke models like NVL72 than for network grid layouts like Google's TPUs, where a single failed device would cause non-trivial issues with network routing.

As previously mentioned, the security of the guarantee processor and the measurements it makes is dependent on the secure enclosure boundary. A Guarantee Processor on the accelerator chip that makes chip-level measurements could potentially be protected with a chip-scale secure enclosure. This has the advantage that it can be included early in the supply chain. It would also likely require advanced tooling (like a focused ion beam machine) to physically tamper with logic on the chip. A defense in depth approach is probably useful here, because the addition of a larger secure enclosure could make it more difficult for attackers to get tooling into place to tamper with the chip enclosure.

To summarize, there are many options for adding secure enclosures to accelerators, with different tradeoffs. Based on the public literature, it is very difficult to circumvent the best secure enclosures. However, nation-state attackers can likely compromise the best current secure enclosures, but it is difficult to estimate what the marginal per-device cost of circumvention would be.

# Interlock-Based FlexHEG Design

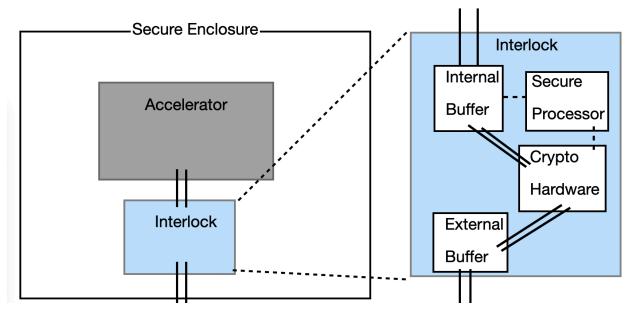

Figure 4: Interlock-based flexHEG design

As previously discussed, integrating flexHEG with core accelerator functionality would make it harder for attackers to spoof data or circumvent guarantees. One promising approach is to position a component on the main data path. We refer to a flexHEG component sitting on the data path as an "Interlock."

A high-level visualization of this design is shown in Figure 4. While the figure shows a single accelerator with a single interlock in a secure enclosure, multiple accelerators could alternatively be held within each secure enclosure. As the only path for data and instructions to enter the accelerator, the interlock would be able to robustly monitor and/or control this flow.

The interlock can use encryption to protect the data that leaves the secure enclosure from being read or modified by an attacker. By controlling the key exchange process used to initialize encrypted channels between nodes, the Guarantee Processor would have clear visibility into the cluster configuration.

Understanding data flows between accelerators is very important for making high-level guarantees about distributed workflows (as each accelerator in isolation may appear to be doing standard matrix multiplications). Using an Interlock is a relatively straightforward way for the guarantee processor to see how data is moving between accelerators. Although, if needed, there are other options to check the authenticity of incoming data, such as comparing the logs of data in memory between accelerators.

A downside of having the Interlock on the main data path is that performance requirements are higher, and it may be required to upgrade to meet future performance requirements (compared to a passive measurement device that doesn't need to be modified as frequently). The ideal implementation would have direct access to a simple part of the data path, like a buffer, and direct control over crypto hardware, but not have to implement all of the logic and performance optimization. An easier to implement/scale version would be for the interlock to not perform the inline encryption, and just be able to read the buffer.

A benefit of the interlock design is that it can treat the accelerator as a black box, with less need to understand or trust internals, which could speed up adaptation to novel accelerators and require less information sharing from accelerator designers. Since the Interlock already sits on a data pathway, it could likely also separately use DMA to read internal accelerator data.

The Interlock could be implemented in several ways, including 1) as an IP block within the accelerator die, 2) as a chiplet sitting near the accelerator die, 3) as a part of high bandwidth memory (HBM), or 4) as a separate component that operates as a network relay or switch. The space constraints for putting the Interlock on-die or near the accelerator chip and HBM are more demanding because this physical layout affects memory latency.

Relatedly, the requirements for Interlock latency and throughput are more demanding the closer the interlock is on the data path to the accelerator die, because accelerators typically access HBM much more frequently than the cluster network (e.g. H100s expect ~3TB/s of HBM data transfer, compared to 900GB/s NVLink, or 128GB/s PCIe to route to the broader network).

# Repurposing the Network Interface Controller

A promising option for a retrofittable Interlock is repurposing or replacing the Network Interface Controller (NIC), which as previously discussed is responsible for communicating with the scale-out network. FlexHEG designs that are external to accelerators are easier to physically retrofit to novel accelerator types, or integrate later in an accelerator design cycle.

This approach draws inspiration from existing security architectures like Amazon's Nitro system [31], which uses the NIC as a hardware-backed security boundary to isolate virtual machines by offloading security-sensitive operations to their Nitro Card.

A potential challenge with updating the NIC is that hyperscalers already have protocols for configuring clusters within their data centers, and custom hardware for network management and encryption. It would likely be possible but costly for them to replace these technologies with a flexHEG version.

# **Encrypted Cluster Formation**

FlexHEG systems need to be able to securely communicate with each other so that they can coordinate around guarantees, and so that data in transit can't be read by adversaries. To enable this, flexHEG systems could follow the encrypted cluster formation protocol described in the table below. This protocol combines public key cryptography for initial authorization with efficient symmetric encryption for ongoing data transfer, allowing clusters to be formed securely while maintaining the high-bandwidth, low-latency communication needed for distributed AI workloads.

- 1. The (directed) network graph of possible communication pairs is initially declared (with unique device IDs for each endpoint).

- 2. The guarantee processor at each node parses this graph to assemble a list of the IDs of all nodes that it needs to send data to.

- 3. Two options for endpoint key lookup:

- a. Logging/approval version: Each guarantee processor sends a request to an external governance system, asking for permission to send data to the list of endpoints, and optionally for any bandwidth or time limits. The governance system sends an approval certificate and the public keys of the requested endpoints.

- b. Decentralized version: each guarantee processor checks a local lookup table<sup>9</sup> for the public keys of the requested endpoints.

- 4. Each guarantee processor randomly generates a session key for AES-GCM encryption and loads it into its output-path crypto engine.

- 5. Each guarantee processor encrypts its session key with the public keys of approved endpoints, then sends this data to those endpoints.

- 6. All guarantee processors decrypt the session keys of source nodes and optionally check for approval to communicate with these nodes (this could be the same certificate from step 3a).

- 7. The approved session keys are loaded into input-path crypto engines to decrypt incoming data.

Besides protecting communication channels, this protocol could optionally provide mechanisms for governance of cluster configurations. If option 3a is chosen instead of 3b, all flexHEG devices could be required to report cluster configurations before starting a workload, which could be a useful level of transparency for international coordination. Routing network approval through a

<sup>&</sup>lt;sup>9</sup> This lookup table would typically be provided by the accelerator manufacturer (Nvidia supports this now for air gapped checks of device attestation [44]). For multilateral use cases it would be helpful to have a multilaterally maintained service. The easiest way to do this would probably be to have each party that monitors the flexHEG manufacturing process publicly share their own table. Third parties could check all tables for consistency.

more centralized service would also reduce the amount of public-key cryptography that needs to be done, which may become significant if direct all-to-all communication is needed in very large clusters.

To allow network switches to run computations on transmitted data (e.g. SHARP [45]), network switches would have to also be set up as flexHEG nodes. They could then decrypt the data, run any computations, then encrypt and transmit the resulting data.

AI workloads frequently involve one-to-many communication, which is why this protocol uses a single symmetric key for each source node (instead of a unique symmetric key for each node pair). A limitation of this is that if one flexHEG node is compromised, the source keys it has could be used to read or spoof transmissions from those source nodes. One way to mitigate the risk of spoofing would be to occasionally sign the hash of previously transmitted hashes using the private key rather than the symmetric key (although care needs to be taken to handle dropped packets sensibly).

# Cryptography Hardware

Cryptography that provides confidentiality could allow the guarantee processor to choose specific accelerators that are allowed to read the outgoing data. Similarly, cryptography that verifies message authenticity could allow guarantee processors to trust that a particular message has come from another guarantee processor.

There are several potential applications of encrypted interconnect, including:

- Protect weights from being exfiltrated by an attacker snooping on interconnect;

- Constrain a training run to only use a certain, limited number of GPUs (similar to Fixed Set [11]) by only allowing specific GPUs to decrypt the information;

- Verify authenticity of metadata describing the compute graph, which could enable verification that training data were approved by a regulator or that model parameters have not exceeded an operation limit.

A common algorithm used to provide Authenticated Encryption with Associated Data [46] is AES-GCM [47]. AES-GCM operates in counter mode, which means encryption of a single data stream can be efficiently parallelized because each block is encrypted separately. A security risk with AES-GCM is that the nonce cannot be re-used even once, as this could allow attackers to infer the secret key [48]. The cipher for AES-GCM can be precomputed prior to seeing the data, and only needs to be XOR'd with the data stream to compute the encrypted output stream. This allows specialized hardware to perform the AES portion of the encryption with close to 0 latency, and then perform the follow-up GCM calculation for authenticity and send this result separately [49].

Order-of-magnitude estimate for fraction of compute needed for 256 bit AES-GCM encryption on an H100:

- H100 capable of 1.98 \*10^15 int8 ops per second;

- Interconnect bandwidth of 900\*10^9 bytes per second;

- ~ 50 operations per byte for AES256;

- AES-256 applies roughly 14 rounds with 4 operations each to all input data, so roughly 50 operations per byte. Authentication with GCM typically takes half the time as the AES component , so we will approximate as roughly 75 operations per byte in total (although exact performance depends a lot on implementation details, and could maybe be accelerated with dedicated hardware)

- So to encrypt all NVLink traffic would require  $900*10^9*75/(1.98*10^15) = ~3\%$  of computing power / energy / board space;

- To encrypt all HBM would require  $3000*10^9*75/(1.98*10^15) = ~11\%$  of power;

- Or to encrypt all PCIe traffic would be  $3000*10^9*75/(1.98*10^15) = ~0.5\%$ ;

To perform the cryptography for authentication and confidentiality, the interlock ideally has a hardware-accelerated crypto engine that supports high bandwidth with minimal latency. An additional benefit of cryptography hardware is that it can be specifically designed to minimize information leakage via side channels that may be exposed by software implementations. Such cryptography engines are common in devices like solid state drives or network cards that need to perform inline encryption (although typically they don't need to support as much bandwidth as is being considered here). Alternatively, this cryptography could potentially be performed by modifying GPU kernels to encrypt data after reading and before writing to HBM, however safe transport of keys would need to be solved.

The NVIDIA H100 can provide encryption of PCIe traffic to support single-GPU confidential computing, although this specific implementation imposes additional latency [50]. Nvidia has suggested that NVLink may be possible to encrypt in Blackwell GPUs, although no public details are available on this at the time of writing.

Inline cryptography hardware is common in modern Network Interface Cards [51], which offer up to 800Gb/s and typically connect accelerators to the frontend or backend network [52]. Modern NICs also typically have general-purpose processors, which are discussed more in the section, A Specific Retrofittable flexHEG Design.

If the interlock does not have enough computational power to encrypt all traffic that passes through it, partial authenticity could be provided at a small fraction of the cost using pseudo-randomized authenticity checks, as described in <u>Appendix C</u>.

# General-Purpose Workload Guarantees

This section discusses approaches to implementing general-purpose verification of guarantees, ranging from simple logging to automated verification of complex guarantees. The feasibility of implementing and securing these approaches for guarantee checking depends on the flexHEG hardware, as discussed previously. The strategies discussed here are presented at a high level because some details depend on the specific type of guarantee. In <u>FLOP Counting</u>, we discuss a more specific design for multi-accelerator guarantees about total FLOPs.

We analyze four potential approaches to verifying claims about computations:

- Transparent logging and auditing: The system maintains detailed logs of all operations, which can be manually audited. This approach is suitable when sharing detailed information about computations is acceptable.

- 2. Automated scanning of unmodified workloads: The system attempts to automatically classify workloads as compliant or non-compliant by analyzing code, usage patterns, and other observable properties.

- 3. Compute graph declaration: Developers make specific claims about their computations, either through upfront static declarations or dynamic operation-by-operation declarations, which the system can verify. The system compiles these declarations into a verified compute graph, which can be more robustly parsed for particular workload guarantees.